Successful installation of the CMS Pixel Tracker

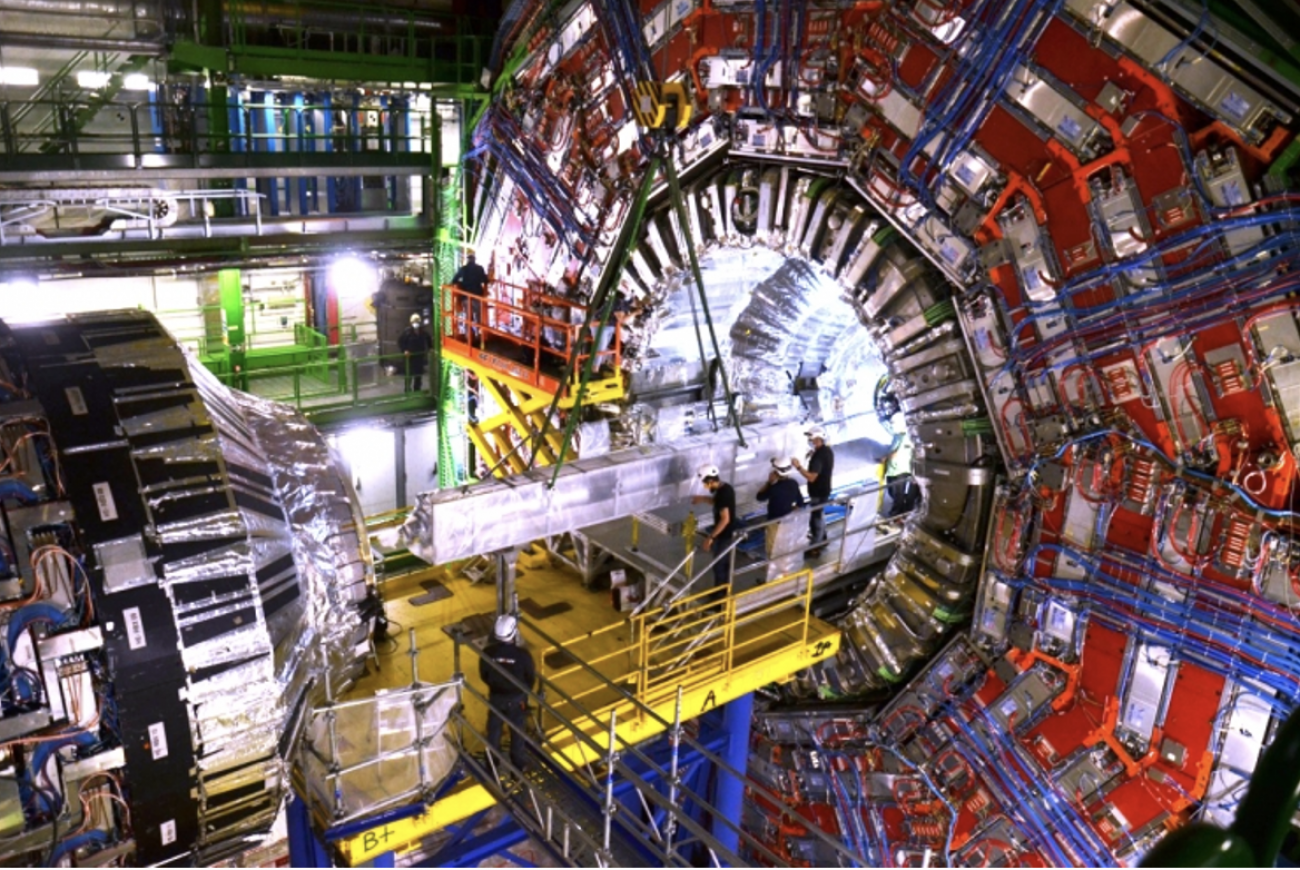

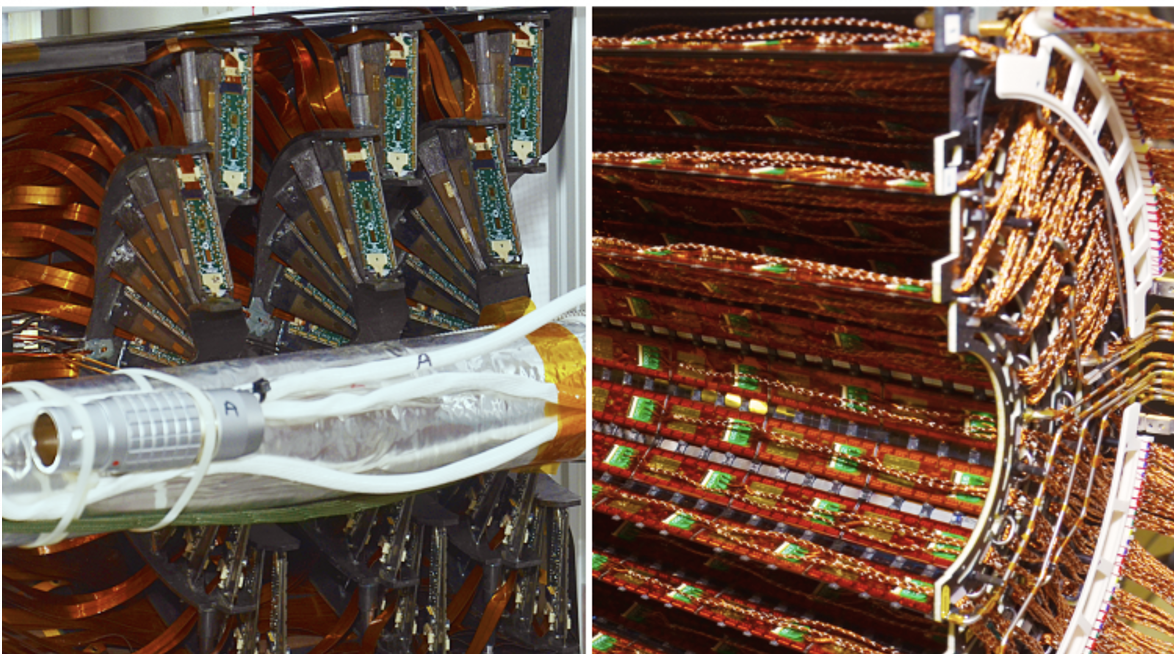

In early 2019 the CMS Phase-1 Pixel detector was extracted from the underground cavern after successful completion of the LHC Run 2 data taking campaign. Its sub-detectors, the Barrel Pixel (BPIX) and Forward Pixel (FPIX) detectors, were stored cool and dry in a clean room facility on the surface to protect the silicon sensors during the long shutdown (LS2) in 2019-2021. The detectors were refurbished and repaired during LS2 to improve the quality of the collected data and the operational stabiliy in the next period of the data taking (Run 3). At the end of June 2021, the detectors were installed in their habitual location inside the CMS detector.

Figure 1. Top: The CMS Foward and Barrel Pixel Detectors (the innermost barrel layer is removed in this picture). Credit: Erik Butz.

The CMS pixel detector has the closest active detector elements to the interaction point and therefore suffers most from radiation. To maintain excellent tracking performance and acquire the highest quality data for physics analyses in Run 3, the innermost layer of the barrel sub-detector was replaced with new and improved components. The opportunity of this exchange was also used to improve upon some parts of the current design.

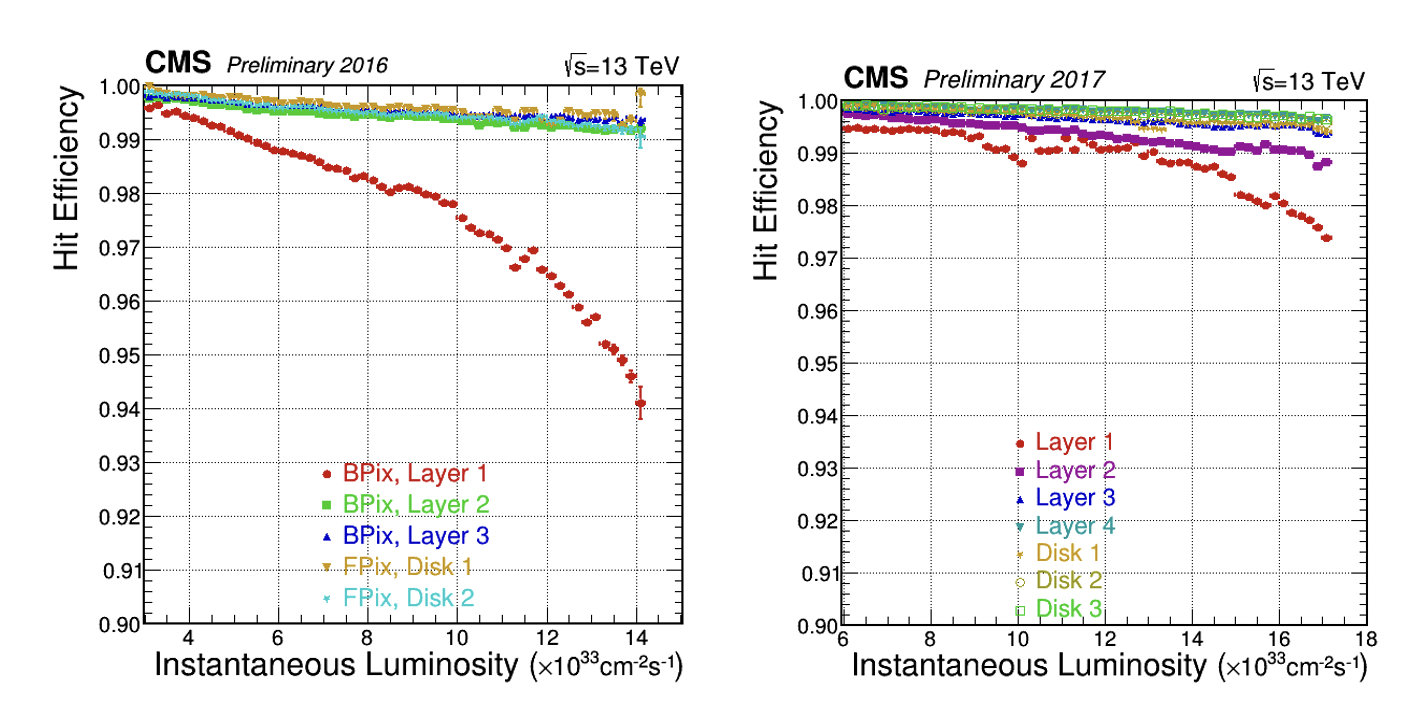

Figure 2. Hit Efficiency as a function of instantaneous luminosity for different layers of the pixel detector. (from CMS Public result). Left: for the original Pixel Detector. Right: for the upgrade Phase-1 Detector (from CMS public result).

The CMS Phase-1 pixel detector was proposed not long after the startup of the LHC in 2010 when it rapidly became clear that the machine would be able to exceed its design instantaneous luminosity by a factor of 2 or more. This meant that the original pixel detector, designed for a luminosity of 1x1034 cm-2s-1, would suffer from large inefficiencies due to the high particle rate close to the interaction point.

The Phase-1 detector was conceived as an evolutionary upgrade, keeping many of the well-tested features of the original system while improving in many regards. The key features of the new detector are the addition of a fourth barrel layer and a third forward disk on either end of the interaction point, a very lightweight mechanical structure, point-of-load DCDC conversion for the low-voltage supply, bi-phase CO2 cooling and an improved readout system designed to cope with instantaneous luminosities of 2x1034 cm-2s-1. As its predecessor, also the upgraded detector is designed to be easily installable and removable. The Phase-1 detector was installed in the Extended Year-End Technical Stop 2016/17 and successfully started taking data in 2017. A major challenge arose in the Fall of 2017 when parts of the DCDC converters started to exhibit failures. Owing to a large effort by many teams from CMS and CERN, the detector was extracted in the YETS 2017/18 and re-installed with fresh DCDC converters. Debugging of the problem by the experts finally revealed a weakness in the FEAST ASIC that has since been addressed. The Phase-1 Pixel detector successfully took data during the last year of Run 2, delivering precise hit measurements for primary and secondary vertexing and for track reconstruction.

The main activity during the LS2 was the installation of a new innermost barrel layer. This replacement had already been anticipated in the initial detector proposal, as radiation damage at this location is most severe and longevity is challenging. During Run 2 undesired features in the front-end electronics were identified that could subsequently be addressed during LS2. The innermost barrel layer detector modules consist of a silicon sensor bump-bonded to 2x8 readout chips (ROCs) designed to cope with particle rates of about 600 MHz/cm2. The initial design of the ROC, the PROC600 ASIC, suffered from a higher than expected noise hit rate and a rare loss of data synchronization in its double-column readout. Several of these shortcomings were mitigated during operations, but nonetheless, an improved version of the ASIC was designed at PSI (Paul Scherrer Institut), Switzerland. This new chip underwent a thorough test process with x-rays, in test beams, and with Heavy Ion beams for Single Event Upset (SEU) generation. All results showed improved performance compared to the previous chip. The other chip on the detector modules, the Token-Bit Manager or TBM, also got an overhaul at Rutgers University as the initial version suffered from SEU-type lockups with higher than expected rates.

Figure 3. Checking the quality of bump-bonding in a clean room at the Helsinki Institute of Physics (Read more)

Of the 150 newly constructed detector modules a total of 96 were finally installed on the mechanical structure, with the bulk of the work happening at PSI. Here, the final assembly of the modules as well as several testing steps were carried out, with help also from colleagues from the Institute Rudjer Boskovic, Croatia, to arrive at the final qualification for the installation in the detector. Some steps were taken care of by other institutes, such as the testing of the bump bonding quality in Helsinki and X-ray testing at the ETH Zurich. The new Layer 1 was fully completed and transported to CERN in the Fall of 2020 and was successfully integrated in the existing detector structure in the Spring of 2021.

Figure: Left: Arrival of the new innermost barrel layer from PSI at LHC P5. Right: mechanical insertion of one half of the new innermost layer. Credit: Erik Butz.

In addition to this replacement, a number of other refurbishment works were carried out on the pixel detector. These included the opportunistic replacement of a few non-functioning modules and the investigation into some poorly performing connections in the barrel detector. The forward pixel detector was equipped with new cooling inlets by CERN and Fermilab for safe handling and a revised high-voltage power distribution scheme built at Fermilab that better matches the low-voltage granularity. Finally, a new set of DCDC converters featuring the latest version of the FEAST ASIC was built at RWTH Aachen, and all DCDC converters were again replaced.

All works were carried out during the very challenging conditions brought upon by the COVID pandemic. After all interventions were complete, the detectors were fully checked out at room temperature and at final operating temperature while still in the surface clean rooms prior to the green light being given for the June 2021 installation.

With the maintenance and upgrade work performed during LS2, the CMS Pixel detector is now in excellent shape for LHC Run 3. Several shortcomings that were found during the initial operation of the detector could be addressed and improved procedures are in place to mitigate any remaining issues. The installation of the pixel detector was followed by an intense period of first checking and subsequent calibration. This work was successfully completed in a few weeks allowing the pixel detector to participate in the CMS CRUZET*) commissioning period. Tracks from cosmic muons were successfully recorded and the data used for further adjustments of the operating parameters such as a relative timing and an initial spatial alignment to the other CMS detectors.